System Verilog 與 Verilog 的關係

標準

當前的System Verilog標準是由IEEE(國際電子電氣工程師協會)和Accellera(基於工業的標準協會)兩個國際組織制定的,版本編號為3。1a,用以表明這個版本是Verilog語言的第3次重大改進。這個版本對System Verilog和Verilog兩個標準都有一些修改。

IEEE標準1800-2005/IEC62530:2007

這個檔案是語言參考手冊(LRM),但其中只包含Verilog標準1364-2005的一些擴充套件的定義。為了得到System Verilog語法的全部定義,SV和V兩種語言的參考手冊(LRM)都是必需的。

IEEE標準1364-2005

這是最新版的Verilog標準,以前曾經有一個2001版本,但是修改的地方不多。

IEEE標準1364-1995

這是最原始的Verilog標準。絕大多數的開源工具只遵循這個原始標準。

IEEE標準1364。1-2002/IEC 62142-2005

這是Verilog RTL綜合標準。這個檔案定義了哪些是可綜合的,哪些是不可綜合的。它的基礎是Verilog標準2001年版。

Accellera Verilog-AMS 2。3-2008

這個檔案是描述模擬數字混合訊號模型的Verilog-AMS語言標準。它的基礎是Verilog標準2005年版。其中Verilog-A子集只包括連續時間元件。建立System Verilog-AMS是Accellera尚未完成的願望。

System Verilog和Verilog之間的差別

System Verilog的基本語法中有一大部分繼承自Verilog。而System Verilog語法集合中新添了一些語法條款,如斷言、類和程式等。本節的宗旨是分析影響RTL硬體建模的兩個Verilog版本有哪些不同,從而瞭解例子應如何修改才能用符合舊標準的模擬和綜合工具。

Verilog 2005

下面的模組是用2005年版Verilog語言編寫的紅綠交通燈狀態機。

由於Verilog 2005 是System Verilog的子集,所以該模組可以用System Verilog編譯器處理,不會出現語法錯誤。

該程式碼段與典型的SystemVerilog程式碼的主要不同點可羅列如下:

always_ff被always所替代。可論證用always_ff是冗餘的,因為在這裡這兩種形式的描述是完全相同的。

always_comb被always@(*)所替代。敏感列表是一個萬用字元,其含義是該塊所有輸入的線網和變數都已自動地包括在內。

logic被reg所替代。在System Verilog中這兩種變數的型別是可以互換的,但是logic清楚地宣告變數是邏輯型別,而reg型別的變數則有可能被錯誤地理解為是一個暫存器。

在Verilog中沒有列舉型別。在Verilog中可以透過宣告一個有足夠多位元位的變數來保持所有這些狀態,然後為每個狀態設定一個引數值(parameter)來代替列舉型別的結構。在這段程式碼裡只有兩個狀態,所以只需要定義一位元的狀態變數就足夠了。若把狀態變數的型別定義為reg[l:0]則可以宣告4個不同的狀態。

沒有定義長度的位串(例如‘0)是不允許的。必須明確指定位串的長度,例如1’b0。

在System Verilog語言中,變數和線網的賦值沒有什麼區別。而在Verilog語言中,變數必須在過程塊中賦值,而線網則必須並且只能在連續賦值語句中賦值。

Verilog1995

下面的程式碼段是用1995年版Verilog語言編寫的紅綠交通燈狀態機。

Verilog1995是Verilog2005的子集,更是System Verilog的子子集。換言之,System Verilog和Verilog-2005都是Verilog-1995的超集。

Verilog-1995與Verilog-2005主要的差別在於以下三點:

不允許使用ANSI C風格的模組頭。換言之,模組的宣告的頭語句中只能包括輸入和輸岀訊號名。埠定義和變數型別必須用另一語句描述。在下面的語句中宣告模組訊號埠形式:input(輸人埠),output(輸岀埠),inout(雙向埠)。最後,必須定義輸出型別為reg預設的型別為wire,因此輸岀訊號需要分三條語句(訊號名、埠、型別)定義。

在敏感或者事件列表中,必須有關鍵字or,不能使用逗號。這個關鍵字or不是布林值的邏輯或操作,而是事件的或。

在敏感列表中,不允許使用萬用字元。必須列出組合過程中的每個輸入。“輸入”包括賦值等號右側的每一個訊號,或者在if和case條件分支語句中,判斷後有可能執行行的每個分支。這裡很可能發生錯誤。若漏寫了某個輸人,模擬在執行時不一定能發現這個問題,但綜合器很可能“糾正”這個錯誤。因此,很可能出現綜合和模擬不一致的情況。

NOW

現

在

行

動

!

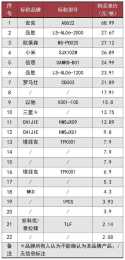

學習Xilinx FPGA最好的資料其實就是官方手冊,下表總結了部分手冊的主要介紹內容,關注我,持續更新中……