ZYNQ PS簡介

ZYNQ 實際上是一個以處理器為核心的系統,PL 只是它的一個外設。Zynq-7000 系列的亮點在於它包含了完整的 ARM 處理器系統,且處理器系統中集成了記憶體控制器和大量的外設,使 Cortex-A9 處理器可以完全獨立於可程式設計邏輯單元。而且實際上在 ZYNQ 中,PL 和 PS 兩部分的供電電路是獨立的,這樣 PS 或 PL 部分不被使用的話就可以被斷電。

在前面我們介紹 SOPC 時提到過,FPGA 可以用來搭建嵌入式處理器,像 Xilinx 的 MicroBlaze 處理器或者 Altera 的 Nios II 處理器。像這種使用 FPGA 的可程式設計邏輯資源搭建的處理器我們稱之為“軟核”處理器,它的優勢在於處理器的數量以及實現方式的靈活性。

而 ZYNQ 中整合的是一顆“硬核”處理器,它是矽晶片上專用且經過最佳化的硬體電路,硬核處理器的優勢是它可以獲得相對較高的效能。另外,ZYNQ 中的硬體處理器和軟核處理器並不衝突,我們完全可以使用 PL 的邏輯資源搭建一個 Microblaze 軟核處理器,來和 ARM 硬核處理器協同工作。

需要注意的是,Zynq 處理器系統裡並非只有 ARM 處理器,還有一組相關的處理資源,形成了一個應用處理器單元(Application Processing Unit,APU),另外還有擴充套件外設介面、cache 儲存器、儲存器介面、互聯介面和時鐘發生電路等。

ZYNQ 處理器系統(PS)示意圖如下所示,其中紅色高亮區域為 APU。

1、APU

如上圖所示是 APU 的簡化框圖。APU 主要是由兩個 ARM 處理器核組成的,每個都關聯了一些可計算的單元:

一個 NEONTM 媒體處理引擎(Media Processing Engine,MPE)和浮點單元(Floating Point Unit,FPU);

一個記憶體管理單元(Memory Management Unit,MMU);

一個一級 cache 儲存器(分為指令和資料兩個部分)。

APU 裡還有一個二級 cache 儲存器,再往下還有片上儲存器(On Chip Memory,OCM),這些是兩個 ARM 處理器共用的。

最後,由一個一致性控制單元(Snoop Control Unit,SCU)在 ARM 核和二級 cache 及 OCM 儲存器之間形成了橋連線。SCU 還部分負責與 PL 對接,圖中沒有標出這個介面。

2、外部介面

如圖 1。4。1 所示,Zynq PS 實現了眾多介面,既有 PS 和 PL 之間的,也有 PS 和外部部件之間的。PS 和外部介面之間的通訊主要是透過複用的輸入/輸出(Multiplexed Input/Output,MIO)實現的,它提供了可以靈活配置的 54 個引腳,這表明外部裝置和引腳之間的對映是可以按需定義的。當需要擴充套件超過 54 個引腳的時候可以透過擴充套件 MIO(Extended MIO,EMIO)來實現,EMIO 並不是 PS 和外部連線之間的直接通路,而是透過共用了 PL 的 I/O 資源來實現的。

PS 中可用的 I/O 包括標準通訊介面和通用輸入/輸出(General Purpose Input/Output,GPIO),GPIO 可以用做各種用途,包括簡單的按鈕、開關和 LED。如下圖所示:

3、儲存器介面

Zynq-7000 APSoC 上的儲存器介面單元包括一個動態儲存器控制器和幾個靜態儲存器介面模組。動態儲存器控制器可以用於 DDR3、DDR3L、DDR2 或 LPDDR2。靜態儲存器控制器支援一個 NAND 快閃記憶體介面、一個 Quad-SPI 快閃記憶體介面、一個並行資料匯流排和並行 NOR 快閃記憶體介面。

4、片上儲存器

片上儲存器包括 256kB 的 RAM(OCM)和 128kB 的 ROM(BootROM)。OCM 支援兩個 64 位 AXI 從機介面埠,一個埠專用於透過 APU SCU 的 CPU/ACP 訪問,而另一個是由 PS 和 PL 內其他所有的匯流排主機所共享的。BootROM 是 ZYNQ 晶片上的一塊非易失性儲存器,它包含了 ZYNQ 所支援的配置器件的驅動。BootROM 對於使用者是不可見的,專門保留且只用於引導的過程。

5、AXI 介面

ZYNQ 將高效能 ARM Cotex-A 系列處理器與高效能 FPGA 在單晶片內緊密結合,為設計帶來了如減小體積和功耗、降低設計風險,增加設計靈活性等諸多優點。在將不同工藝特徵的處理器與 FPGA 融合在一個晶片上之後,片內處理器與 FPGA 之間的互聯通路就成了 ZYNQ 晶片設計的重中之重。如果 Cotex-A9 與FPGA 之間的資料互動成為瓶頸,那麼處理器與 FPGA 結合的效能優勢就不能發揮出來。

Xilinx 從 Spartan-6 和 Virtex-6 系列開始使用 AXI 協議來連線 IP 核。在 7 系列和 ZYNQ-7000 AP SoC 器件中,Xilinx 在 IP 核中繼續使用 AXI 協議。AXI 的英文全稱是Advanced eXtensible Interface,即高階可擴充套件介面,它是 ARM 公司所提出的 AMBA(Advanced Microcontroller Bus Architecture)協議的一部分。

AXI 協議是一種高效能、高頻寬、低延遲的片內匯流排,具有如下特點:

1、匯流排的地址/控制和資料通道是分離的;

2、支援不對齊的資料傳輸;

3、支援突發傳輸,突發傳輸過程中只需要首地址;

4、具有分離的讀/寫資料通道;

5、支援顯著傳輸訪問和亂序訪問;

6、更加容易進行時序收斂。

在數位電路中只能傳輸二進位制數 0 和 1,因此可能需要一組訊號才能高效地傳輸資訊,這一組訊號就組成了介面。

AXI4 協議支援以下三種類型的介面:

1、 AXI4:高效能儲存對映介面。

2、 AXI4-Lite:簡化版的 AXI4 介面,用於較少資料量的儲存對映通訊。

3、 AXI4-Stream:用於高速資料流傳輸,非儲存對映介面。

在這裡我們首先解釋一下儲存對映(Meamory Map)這一概念。如果一個協議是儲存對映的,那麼主機所發出的會話(無論讀或寫)就會標明一個地址。這個地址對應於系統儲存空間中的一個地址,表明是針對該儲存空間的讀寫操作。

AXI4 協議支援突發傳輸,主要用於處理器訪問儲存器等需要指定地址的高速資料傳輸場景。AXI-Lite為外設提供單個數據傳輸,主要用於訪問一些低速外設中的暫存器。而 AXI-Stream 介面則像 FIFO 一樣,資料傳輸時不需要地址,在主從裝置之間直接連續讀寫資料,主要用於如影片、高速 AD、PCIe、DMA 接 口等需要高速資料傳輸的場合。

在 PS 和 PL 之間的主要連線是透過一組 9 個 AXI 介面,每個介面有多個通道組成。這些形成了 PS 內部的互聯以及與 PL 的連線,如下圖所示:

上圖給出了每個介面的簡述,標出了主機和從機(按照慣例,主機是控制匯流排併發起會話的,而從機是做響應的)。需要注意的是,介面命名的第一個字母表示的是 PS 的角色,也就是說,第一個字母 “M”表示 PS 是主機,而第一個字母“S”表示 PS 是從機。

上圖中 PS 和 PL 之間的 9 個 AXI 介面可以分成三種類型:

1、通用 AXI(General Purpose AXI):一條 32 位資料匯流排,適合 PL 和 PS 之間的中低速通訊。介面是透傳的不帶緩衝。總共有四個通用介面:兩個 PS 做主機,另兩個 PL 做主機。

2、加速器一致性埠(Accelerator Coherency Port):在 PL 和 APU 內的 SCU 之間的單個非同步連線,匯流排寬度為 64 位。這個埠用來實現 APU cache 和 PL 的單元之間的一致性。PL 是做主機的。

3、高效能埠(High Performance Ports):四個高效能 AXI 介面,帶有 FIFO 緩衝來提供“批次”讀寫操作,並支援 PL 和 PS 中的儲存器單元的高速率通訊。資料寬度是 32 或 64 位,在所有四個介面中 PL 都是做主機的。

上面的每條匯流排都是由一組訊號組成的,這些總線上的會話是根據 AXI4 匯流排協議進行通訊的。

*宣告:本文於網路整理,版權歸原作者所有,如來源資訊有誤或侵犯權益,請聯絡我們刪除或授權事宜。

‧

‧

‧

‧

‧

‧

‧

‧

‧

‧

‧

‧

‧

‧

‧

‧ END

‧‧‧‧‧‧‧‧‧‧‧‧‧‧‧‧

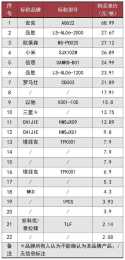

學習Xilinx FPGA最好的資料其實就是官方手冊,下表總結了部分手冊的主要介紹內容,關注我,持續更新中……