文︱

郭紫文

圖︱

網路

超越臺積電,是三星一直以來的夢想。早在2017年三星晶圓論壇上,其相關負責人便揚言,三星要超越聯電和格芯,晉升為全球晶圓代工第二名,未來還要擠掉臺積電,成為代工市場龍頭。超越聯電和格芯的目標於2018年便已實現,而與臺積電的差距卻始終難以跨越。

在工藝製程不斷演進的過程中,越來越多的參與者被淘汰出局,如今先進製程玩家僅剩下臺積電、三星和英特爾三家公司。為了追趕臺積電,三星在先進製程的佈局上略顯激進。在資本支出方面,2021三星晶片業務資本支出超360億美元,超越同年度臺積電的投資規模。而在先進工藝研發方面,三星也欲搶先臺積電,實現3nm晶片量產,並率先採用GAA工藝。

然而,三星的鉅額投資似乎並未取得預想成效。前段時間,三星晶圓代工被曝出“良率造假”,正深入調查資金流向及產量報告等問題,重點關注5nm至3nm良率。造沒造假不得而知,但三星深陷良率泥潭久矣,4nm良率僅為35%,反觀臺積電4nm製程工藝晶片的良率可達到70%,是三星的兩倍。正因為良率問題,三星晶圓代工的主要客戶正在流失。高通決定將驍龍8 Gen1訂單轉向臺積電生產,後續3nm晶片也全量委託給臺積電;英偉達RTX 40系列顯示卡也將採用臺積電5nm製程。

在此境況下,三星離晶圓代工第一把交椅漸行漸遠。為了挽回局面,三星近期也是動作頻頻。據韓媒報道,三星電子日前調整了其組織架構,設立測試與封裝中心,企圖擴大封測領域投資佈局力度。另外,在先進製程上的失利,讓三星開始考慮提高其成熟工藝產能,以進一步最佳化產能與成本,提高晶片代工營收,增強市場競爭力。

爭奪先進製程,良率是關鍵

相較於臺積電,2005年才踏入晶圓代工業務的三星無疑是後進者。此後十餘年內,三星晶圓代工業務一路披荊斬棘,超越了格芯、聯電等前排廠商,逐漸比肩臺積電。事實上,據IC Insights資料顯示,截至2009年之前,三星晶圓代工業務營收尚未超出4億美元,市場佔有率很低。

進入2011年,三星的研發實力逐漸開始突顯。在28nm成熟製程,三星於2012年實現量產,並於次年匯入了28nm HKMG工藝。在此方面,臺積電僅比三星領先一年,而聯電與格芯28nm製程於2013年才開始量產。

隨後,工藝製程演進至14nm及以下先進節點,聯電宣佈退出14nm FinFET以下先進製程技術研發,格芯也放棄了12nm以下先進製程技術投入。在晶圓代工市場上,僅剩下臺積電、英特爾、三星以及中芯國際等廠商還在推進先進製程的演進。自2017年晶圓代工業務獨立以後,三星與臺積電在先進製程上的競爭也越來越焦灼。從量產時間來看,在7nm及以下工藝製程,三星與臺積電你追我趕,不分伯仲。

圖:三星先進製程演進

然而從DigiTimes資料可以看出,各個廠商對工藝製程的定義並沒有統一的標準,單從電晶體密度看,三星3nm工藝製程還不如英特爾7nm(已改為Intel 4)。三星3nm工藝製程電晶體密度達1。7億顆/平方毫米,而臺積電5nm工藝製程電晶體密度達1。73億顆/平方毫米,英特爾7nm工藝製程電晶體密度達1。8億顆/平方毫米。但電晶體密度僅作為衡量半導體工藝水平的一個參考,具體到應用中,還需要從材料、功耗、效能表現、成本、良率等多方面進行考量。

對於半導體制造,良率直接關乎著晶片量產成本,對產品品質和可靠性也有一定影響,同時也牽涉著客戶信任度和滿意度。良率越高,每片晶圓上質量合格晶片數量就越多,每顆晶片的成本就越低。因此,對三星而言,電晶體密度追不上臺積電並不是重點,關鍵是如何解決良率問題。相比之下,三星4nm製程良率約35%,而臺積電同製程良率則為70%,這意味著三星的晶圓代工成本將高於臺積電兩倍不止。而良率造成的成本上升,直接勸退了高通、英偉達在內的主要客戶。

在先進製程爭奪戰中,良率是一個很關鍵的因素。而工藝製程越是先進,工藝難度越高,良率越是難以保障。影響良率的因素多種多樣,從晶圓製造到封裝測試,半導體制造每個流程都有可能造成晶片良率損失。顯然,單在良率方面,三星便落了臺積電一大截。若想超越臺積電,三星首先要解決的便是先進製程的良率問題。

轉戰先進封裝和成熟製程,搶先佈局GAA工藝

在追趕臺積電的過程中,三星因良率問題遭到了客戶信任危機。然而,其對先進製程的激進策略並沒有止步。在3nm工藝製程上,臺積電仍基於FinFET工藝,而三星則率先轉向了GAA電晶體工藝。三星表示,該公司將按照時程在2022年下半年領先全球推出商用GAA晶片工藝。據報道,三星擬於2022年上半年完成3nm GAA工藝質量評估,並計劃於今年6、7月份在韓國平澤市P3工廠開工建設3nm晶圓廠。

作為FinFET的繼任者,GAA(全環繞柵極)電晶體在效能、功耗、靜電特性方面都有著顯著提升。同等尺寸結構下,GAA的溝道控制能力比FinFET更強,為尺寸進一步微縮提供了可能性。三星也表示,與7nm工藝製程相比,3nm GAA工藝邏輯面積效率提高45%,功耗降低50%,效能提高了35%。

然理論引數效能的提升並不意味著可以滿足客戶在效能產能及良率方面的需求。韓國遠大證券顯示,截至2020年,三星晶圓代工IP不超過1萬項,而臺積電IP數則已經達到3。5萬至3。7萬項。在3nmGAA工藝相關IP方面,三星相對落後於臺積電。這也讓業界對三星在3nm GAA工藝中的良率及效能表現充滿了質疑。

整體而言,客戶流失、IP匱乏等問題都將使三星的工藝演進面臨巨大挑戰。要知道,在晶圓代工領域,資本投入、技術和經驗將形成正向迴圈,代工廠以鉅額投資驅動技術迭代,從而換取客戶資源,而後透過客戶量產經驗提升良率,從而反哺企業進行下一代技術研發。這就不難理解晶圓代工領域為何會形成寡頭壟斷格局了。

在先進製程繼續發力的同時,三星也在轉變思路,考慮提高成熟工藝製程的產能,不斷最佳化和改進舊制程,提高產品效能和成本競爭力。去年10月,三星對17nm FinFET工藝製程技術進行了升級最佳化,並將其應用於原本28nm製程生產的影感測器和行動顯示驅動晶片(DDI)的生產中,進一步提高了生產效率。

除此之外,三星還與英特爾、臺積電等企業參與成立了Chiplet標準聯盟UCIe,並設立測試與封裝中心,加碼先進封測領域技術投資。隨著摩爾定律式微,新材料、新工藝、新架構逐漸成為延續摩爾定律的關鍵,異構整合與先進封裝也將成為未來發展的主流趨勢。可以看到,晶圓代工領域的頭部廠商們都將先進封裝及測試作為一大戰略方向。

臺積電在先進封裝領域佈局已久,2020年,臺積電推出了3DFabric技術平臺,該技術平臺包含臺積電前端晶片堆疊SoIC技術和後端先進封裝CoWoS和InFO技術。

相對而言,三星在先進封裝領域的技術實力較為薄弱。2020年,三星宣佈其3D封裝技術X-Cube;去年11月,三星又推出了全新2。5D封裝解決方案H-Cube(混合基板封裝)。為在後摩爾時代繼續提高晶片效能,三星未來將加大先進封裝投資力度,提高先進封裝技術研發實力。

總結

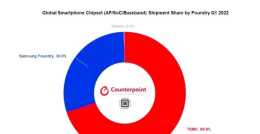

據TrendForce集邦諮詢資料,2021年第四季度,臺積電營收達157。5億美元,市佔率52。1%,三星則為55。4億美元,市佔率18。3%,有著不小的差距。隨著今年資本支出不斷飆升(臺積電2022年資本支出預計提升至400至440億美元;三星預計2022年資本支出320億美元),預計晶圓代工市場競爭將更加激烈。

另一方面,在2nm工藝節點上,臺積電也將轉向GAA工藝,而英特爾則計劃在Intel 20A工藝改用GAA電晶體(英特爾稱RibbonFET電晶體)。現階段,英特爾宣佈開放代工服務,並收購了高塔半導體。屆時,在2nm工藝製程爭奪戰中,三星將與臺積電和英特爾正面“廝殺”。