To maintain and strengthen TSMC’s technology leadership, the Company plans to continue investing heavily in R&D。 For advanced CMOS logic, the Company’s 3nm and 2nm CMOS nodes continue to progress in the pipeline。 In addition, the Company’s reinforced exploratory R&D work is focused on beyond-2nm node and on areas such as 3D transistors, new memory and low-R interconnect, which are on track to establish a solid foundation to feed into technology platforms。

以上一段是摘自臺積電官網的未來研發計劃,從這段描述中可以看出,臺積電劍指2nm,甚至更先進的工藝。在逼近物理極限的情況下,新工藝研發的難度以及人力和資金的投入,也是呈指數級攀升。在如此艱難的背景下,臺積電的底氣何在?我認為有如下三點:

當前的先進工藝節點只是商業代號,而非Gete Lenth或Half-Pitch

如果有人問晶片工藝的中的7nm、5nm指什麼?那麼我相信很多人都能給出答案——電晶體導電溝道的長度或者柵極寬度,並且很多人也知道,當前的7nm、5nm只是等效工藝節點,而非真正的溝長或者柵寬。

如果進一步問一下這個問題,當前5nm工藝真正的導電溝長或者柵寬是多少呢?恐怕很多人回答不出來了。不賣關子了,IEEE給出的半導體工藝road map資料是比較可信的,從下圖中我們可以看到不同時間對應的工藝節點,而這表裡對當前工藝節點的英文描述則非常有意思,它沒有用“technology nodes”而是用Logic industry “Node Range” Labeling。

一個Labeling可以說準確的表達了工藝命名的現狀。

所以從上表中,我們可以看到,5nm工藝節點的Gate Lenght為18nm、3nm為16nm、2。1nm為14nm、1。5nm/1。0nm/0。7nm則均為12nm。在十幾奈米的尺度短溝道效應可以用多種手段來克服,而量子隧穿效應並不明顯,所以說,

臺積電說自己在2030年將擁有1nm Labeling的晶片,我也完全相信。

事實上,從積體電路發明以來,工藝節點的定義也在不斷髮生變化,從最初的Gate Length到現在,幾乎拋棄了各種真實引數Gate Length/Half Pitch/Fin Pitch等。雖然當前的工藝命名背離了真實的工藝,但對於臺積電、三星等商業公司來說,顯然從工藝命名上獲得了巨大的商業上的利益和成功。

此為底氣一。

Evolving Industry Node definitions 來源:INTERNATIONAL ROADMAPFORDEVICES AND SYSTEMS

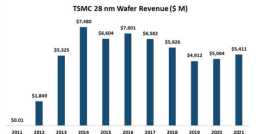

雄厚的資金及資源加持

半導體產業鏈各個環節是非常緊密的,而現階段全球的半導體巨頭也組成了一個巨大的利益共同體。

臺積電擁有最先進的EUV光刻機

工欲善其事必先利其器,光刻機作為半導體制造中最重要的裝置,擁有與否則決定了一家Fab的工藝上限。

一臺最先進的EUV光刻機價值近10億,而研發EUV光刻機的投入更是天文數字。除了ASML,製造光刻機還有兩家公司——尼康和佳能,但這兩家都因為投入太高而放棄研發。

EUV光線的能量、破壞性極高,製程的所有零件、材料,樣樣挑戰人類工藝的極限。例如,因為空氣分子會干擾EUV光線,生產過程得在真空環境。而且,機械的動作得精確到誤差僅以皮秒(兆分之一秒)計。「如果我們交不出EUV的話,摩爾定律就會從此停止,」ASML總裁暨執行長溫彼得(Peter Wennink)說。因此,五年前,才會出現讓ASML聲名大噪的驚天交易——英特爾、臺積電、三星等彼此競爭的三大巨頭,竟聯袂投資ASML41億、8。38億、5。03億歐元。

反過來,臺積電也從ASML可以訂購到EUV光刻機,進行新工藝的研發和產能的擴充。

臺積電擁有最有錢的客戶

但說到TSMC每一代最先的工藝,總少不了一位特殊的客戶,那就是蘋果。

5nm,3nm甚至是2nm技術都是由蘋果和臺積電在共同研發,因此蘋果在臺積電先進工藝的產能擁有牢不可破的地位,將會獨佔業界最先進的工藝一段時間,吃盡製程紅利。

同時蘋果也是臺積電最大的客戶,去年為臺積電貢獻了782。8 億人民幣的營收。

此為底氣二。

2025年?三星也可以!

在今年10月份的三星代工論壇2021大會上,三星披露了最新的工藝進展和路線圖。

三星代工市場策略高階副總裁MoonSoo Kang透露,2GAP工藝會在2025年量產。

隨著FinFet電晶體結構潛力被挖掘殆盡,未來3nm和2nm將採用GAA電晶體以及2。5D/3D堆疊技術,以實現更好的溝道控制的同時降低功耗。

新技術則為三星臺積電的底氣三。

電晶體的演進

為什麼要追求先進工藝?

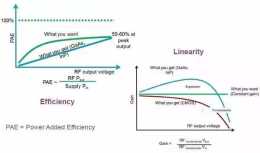

製程工藝的提升,可以帶來更高的電晶體密度、更強的效能以及更低的功耗。

我們再回歸到工藝製程的原始定義,即晶片7nm,5nm工藝中的7nm,指的是電晶體導電溝道的長度,通常也認為是電晶體的柵極寬度。

那麼這個Gate的寬窄為什麼會影響效能和功耗呢?先說效能,效能好意味著在一定的時間幹更多的事,在處理器裡就是更多的運算,我們可以當半導體電晶體每次0/1變化就算一次運算,那麼那個紅色Gate越寬,兩個綠色電極就越遠,導致他們直接連通一次的時間就會越長。這就好比一個人在10分鐘裡做25m往返跑的次數肯定比50m往返跑的次數多一樣。所以Gate越小,電晶體一次狀態變化的所需時間就會越短,單位時間的工作次數就會越多,一堆電晶體單位時間可做的運算自然就更多,所以效能更好。

再說說功耗。Gate是透過加電壓幫助兩個綠色電極通電的,而Gate越寬,就需要更高的電壓才能導通兩極,Gate越窄,導通就更容易,所需的電壓也就越低。

而做晶片則是效能,功耗,面積和成本的平衡藝術。如果製程工藝的提升能讓晶片在這幾方面都更進一步,那麼在工藝上投入大量的研發資則是可以理解的。

所以綜合以上幾個原因,臺積電作為半導體制造環節的巨頭,2025年量產2nm是有底氣的。在摩爾定律放緩的今天,More Moore、More than Moore、Beyond CMOS等新概念層出不窮,為摩爾定律續命。在未來十年,半導體工藝製程依然有相當大的提升空間,所以關於半導體是夕陽產業的論調可以休矣!